中央大学の研究グループは,大容量で低コストな3D NANDフラッシュメモリにおける垂直方向の電荷の移動がメモリセルの信頼性を劣化させることを明らかにした。そして電荷移動を抑制する手法を開発し,データ保持中のメモリのエラーを40%削減し,メモリがデータを保持できる時間を2.8倍に増加させることに成功した(ニュースリリース)。

中央大学の研究グループは,大容量で低コストな3D NANDフラッシュメモリにおける垂直方向の電荷の移動がメモリセルの信頼性を劣化させることを明らかにした。そして電荷移動を抑制する手法を開発し,データ保持中のメモリのエラーを40%削減し,メモリがデータを保持できる時間を2.8倍に増加させることに成功した(ニュースリリース)。

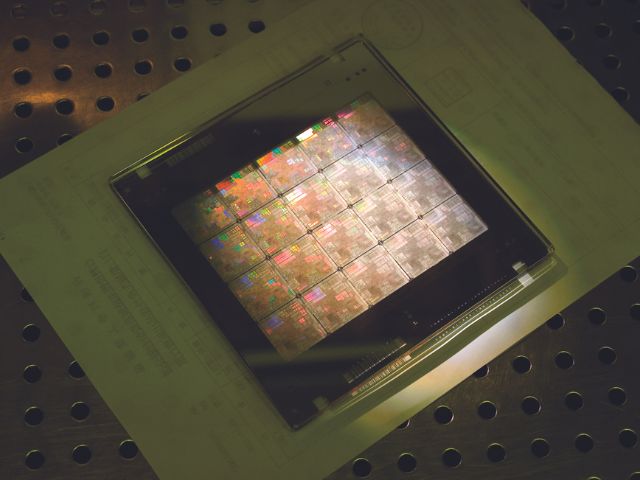

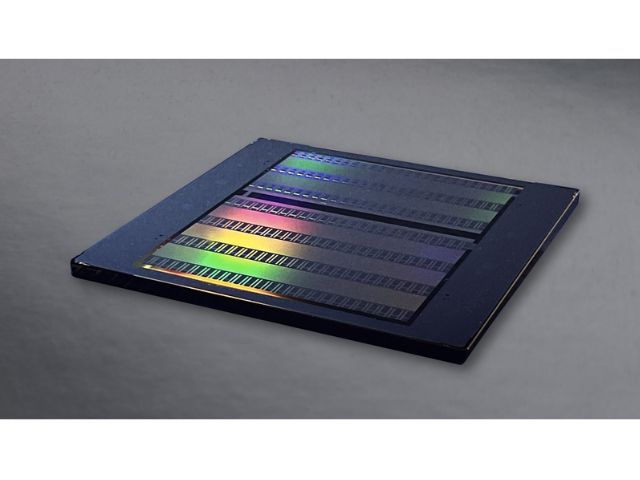

2次元のNANDフラッシュメモリに対し,3D NANDフラッシュでは,上下のメモリセルで電荷蓄積層がつながっているため,垂直方向の電界によって隣のメモリセルに電荷が移動し,やがて記憶したデータが失われる問題がある。

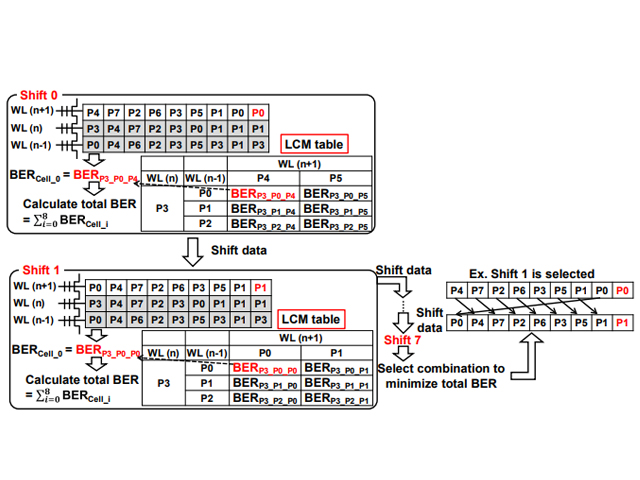

特に1個のメモリセルに3ビットの情報を記憶することで大容量を実現する TLC(Triple-Level Cell)セルでは,8個のしきい値電圧の状態(P0~P7)が存在し各状態間の間隔が小さくなることから,電荷移動によって不良になりやすいという問題がある。

研究では3D NANDフラシュメモリに固有な不良の現象として,隣接するメモリセル間のしきい値電圧の差が大きくなるほど垂直方向の電界が強くなり,その結果電荷移動によりしきい値電圧が大きく変化して不良になってしまう事を明らかにした。

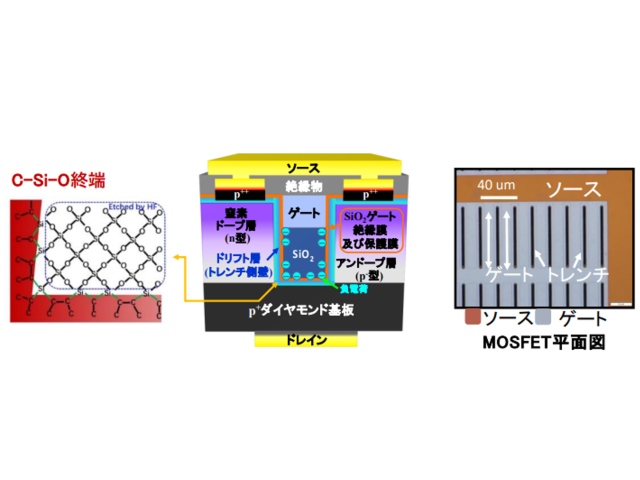

この垂直方向の電荷の移動を抑制するため,研究グループは「VTH Nearing」を開発した。この手法はSSDの中のフラッシュメモリを制御するSSDコントローラに搭載される。提案の制御手法では,電荷の移動が一番小さくなるシフト量を選択することで,上下のメモリセルのしきい値電圧を近づけることに成功した。

これにより,垂直方向の電界が小さくなり,結果として電荷移動を抑制することに成功した。その結果,データ保持中のメモリセルのエラーを40%削減し,データ保持の寿命を2.8倍に伸ばすことに成功した。

3D NANDフラッシュメモリに固有の電荷の移動は,今後メモリセルのサイズが縮小され大容量化されると更に悪化することが予想される。VTH Nearingにより電荷移動に起因するデータ損失を防ぎ,3D NANDフラッシュメモリを大容量化する上での問題の1つを克服することができる。

研究グループは今後,大容量のメモリを必要とするクラウドデータセンターの記憶媒体としての使用が期待できる成果だとしている。